不要认为沿信号简单,就不拿他当回事。以下两种情况不知道大家遭遇过没有。

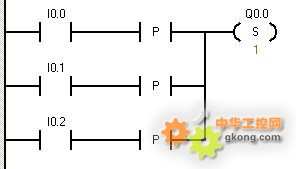

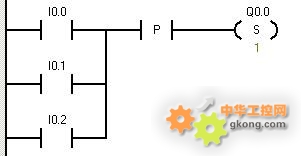

1.感觉图1写的逻辑段有点啰嗦,干脆改写成图2的简洁模样。其实两者有区别,不可以将图1简化写成图2。

图1中三个开点的上升沿相互独立,互不影响,任一个上升沿都会置位Q0.0;图2中如果有一个开点一直闭合,那么另外两个开点的上升沿就不会让Q0.0置位。

图1

图2

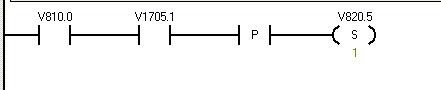

2.不要习惯性将图3网络段的逻辑解读成V810.0=1时V1705.1上升沿输出逻辑。

多个节点串联后取上升沿,实质检测的是串联块上升沿,不是单个节点上升沿。图3网络段还要考虑V1705.1=1的情况下V810.0上升沿,或者V1705.1和V810.0两者同时上升沿的极限情况。

图3

上升沿其实存储的是前段程序的RLO,即逻辑运算结果。

图一中三个上升沿分别存储的是I0.0,I0.1,I0.2边沿状态,而对于图二,上升沿存储的是I0.0 OR I0.1 OR I0.2的边沿状态,显然,通过或运算,RLO的值是不同的。

对于图三也是如此:RLO的结果是V810.0 AND V1705.1,而上升沿存储的是RLO的结果,在单CPU的PLC中,受限于程序扫描方式,不会出现同时上升沿的这种状况,切换到STL方式就很好理解了。

Good Luck~

图一中三个上升沿分别存储的是I0.0,I0.1,I0.2边沿状态,而对于图二,上升沿存储的是I0.0 OR I0.1 OR I0.2的边沿状态,显然,通过或运算,RLO的值是不同的。

对于图三也是如此:RLO的结果是V810.0 AND V1705.1,而上升沿存储的是RLO的结果,在单CPU的PLC中,受限于程序扫描方式,不会出现同时上升沿的这种状况,切换到STL方式就很好理解了。

Good Luck~

18-05-10 15:05