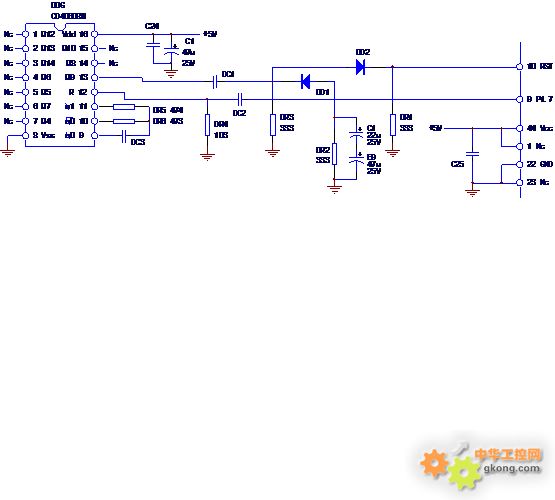

这是一个高电平信号复位电路,用2进制串行计数器/分频器CD4060等元件组成。请大家讨论一下复位控制过程,并帮忙分析一下,此测绘电路是否有错误?

先谢谢大家。

如果电路是对的,工作过程可能是这样的,上电后,CD40609、10、11脚内部振荡电路开始工作,经分频从Q9输出脉冲信号,其高电压时间应满足CPU的2个时钟周期以上,经DC1耦合至CPU的RST复位脚,向9脚发送一个高电平的上电复位脉冲。CPU工作后,从9输出一个高电平脉冲,经DC2耦合,至CD4060的12脚,使内部计数器清零。

但此后,CD4060被复位后,DC2上电荷经DR4泄放,CD4060应该产生计数输出,会再次形成对CPU的复位动作,这是不允许的!好像不对啊。另外,13脚外接DC1、DD2、C1、E9电路作用是什么?好像起不到什么作用啊?

是否CD4060接受复位信号后(12脚复位信号只是个瞬态信号啊),能保持清零动作吗,有锁存功能吗?假使能保持复位状态,那又如何清除其复位状态?

没有查到相关资料,只有求助各位了。希望能尽快见到回复!有使用和熟悉该芯片的朋友,回复一下吧。

先谢谢大家了!

最后修改:2011/3/12 16:23:30